## Quiz 2

(October 4<sup>th</sup> @ 5:30 pm)

## PROBLEM 1 (35 PTS)

• Complete the following table. Use the <u>fewest</u> number of bits in each case:

| REPRESENTATION |                    |                |                |

|----------------|--------------------|----------------|----------------|

| Decimal        | Sign-and-magnitude | 1's complement | 2's complement |

|                |                    | 101010         |                |

| -16            |                    |                |                |

|                |                    |                | 100001         |

|                | 0100000            |                |                |

■ Convert the following decimal number to its 2's complement representation: -17.375 (5 pts)

## **PROBLEM 2 (30 PTS)**

Perform the following operations in the 2's complement representation, i.e., provide the summands and the result in 2's complement representation. Use the minimum number of bits to represent both the summands and the result so that the overflow bit is 0.

## **PROBLEM 3 (35 PTS)**

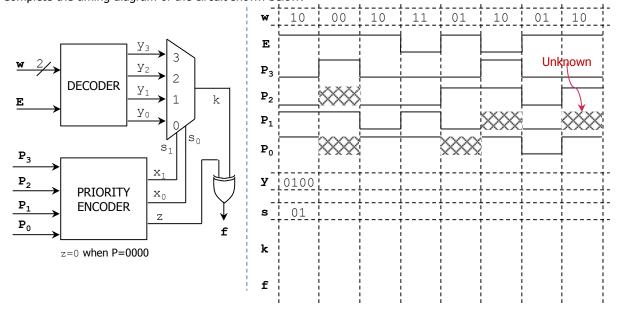

• Complete the timing diagram of the circuit shown below:

1